# **QPHY-DDR4**DDR4, LPDDR4 and LPDDR4X Serial Data Compliance Software

# **Instruction Manual**

November, 2023

Relating to:

MAUI® version 10.5.x.x and later

QualiPHY® version 10.5.x.x and later

700 Chestnut Ridge Road Chestnut Ridge, NY, 10977-6499 Tel: (845) 425-2000, Fax: (845) 578 5985 teledynelecroy.com

© 2023 Teledyne LeCroy, Inc. All rights reserved.

Customers are permitted to duplicate and distribute Teledyne LeCroy documentation for internal training purposes. Unauthorized duplication is strictly prohibited.

Teledyne LeCroy and other product or brand names are trademarks or requested trademarks of their respective holders. Information in this publication supersedes all earlier versions. Specifications are subject to change without notice.

QualiPHYDDR4Manual.pdf November, 2023

# **Table of Contents**

| Introduction                                          |   |

|-------------------------------------------------------|---|

| Conventions                                           | 1 |

| Technical Support                                     | 2 |

| Software Installation and Setup                       |   |

| Oscilloscope Requirements                             | 3 |

| Update Oscilloscope Firmware                          | 4 |

| Install QualiPHY Application                          | 4 |

| Activate QualiPHY Components in MAUI                  |   |

| Activate Other Teledyne LeCroy Software               |   |

| Set Up Remote Control (optional)                      |   |

| Set Up Dual Monitor Display (optional)                |   |

| Set Up the QualiPHY Application                       |   |

| DDR4/LPDDR4 Testing                                   |   |

| Required Hardware                                     |   |

| Test Preparation                                      |   |

| Test Initiation                                       |   |

| DDR4 and LPDDR4/4X Test Configurations                |   |

| DDR4 and LPDDR4/4X Test Descriptions                  |   |

| DDR4 and LPDDR4/4X Variables                          |   |

| DDR4 and LPDDR4/4X Limit Sets                         |   |

| Using QualiPHY                                        |   |

| QualiPHY Test Process                                 |   |

| Generating Reports  Customizing QualiPHY              |   |

| X-Replay Mode                                         |   |

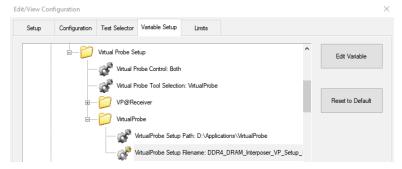

| Appendix A: Virtual Probing Setup and Dependencies    |   |

| Virtual Probing Methods                               |   |

| Method 1-VirtualProbe@Rcvr Math Functions             |   |

| Method 2-Virtual Probe Software                       |   |

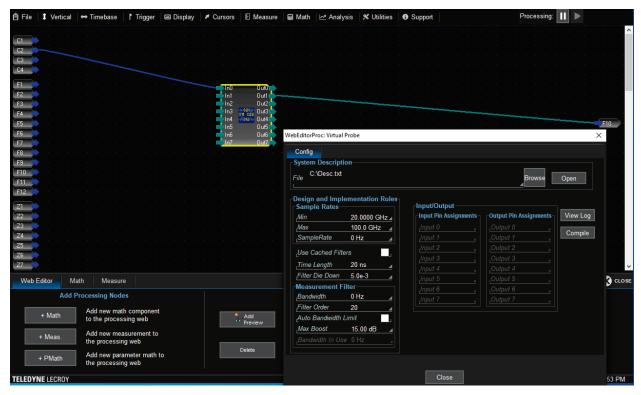

| Method 3-WebEditor                                    |   |

| Appendix B: File Name Conventions for Saved Waveforms |   |

| Appendix C: Common Warning Messages                   |   |

| Appendix C. Common warming wessages                   |   |

# **Table of Figures**

| Figure 1. Memtest86+ software                                                                          | 12 |

|--------------------------------------------------------------------------------------------------------|----|

| Figure 2. Choose to analyze Read or Write burst types only                                             | 13 |

| Figure 3. Verification of CK signal                                                                    |    |

| Figure 4. DDR4 Signal Phase verification (Write out of phase, Read in phase)                           | 14 |

| Figure 5. Amplitude can help validate if different burst packets are present.                          | 15 |

| Figure 6. Verification of Idle levels.                                                                 |    |

| Figure 7. Oscilloscope configuration after tCK, tCH, tCL and tJIT(duty) tests                          | 22 |

| Figure 8. Oscilloscope configuration after tJIT(per) and tJIT(per)_dj tests                            | 24 |

| Figure 9. Oscilloscope configuration after tJIT(cc) tests.                                             | 25 |

| Figure 10. Oscilloscope configuration after tERR(2per), tERR (3per), tERR (4per) and tERR (5per) tests | 26 |

| Figure 11. Oscilloscope configuration after Write Bursts (Inputs) - DQ and DQS Eyes                    |    |

| Figure 12. Oscilloscope configuration after DQ Write Input Compliance Mask test                        | 29 |

| Figure 13. Oscilloscope configuration after VIHL_AC test.                                              |    |

| Figure 14. Oscilloscope configuration after Read Bursts (Outputs) test                                 | 31 |

| Figure 15. Oscilloscope configuration after the tDVAC test                                             |    |

| Figure 16. Oscilloscope configuration after SRIdiff_CK test                                            | 34 |

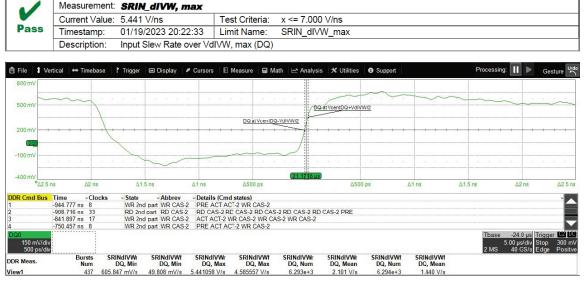

| Figure 17. Oscilloscope configuration after SRIN_diVW, max test                                        | 35 |

| Figure 18. Oscilloscope configuration after Overshoot Peak Amplitude test                              | 36 |

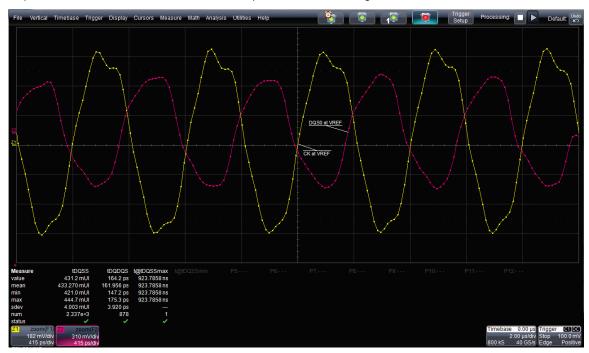

| Figure 19. Oscilloscope configuration after the SRQ test.                                              | 38 |

| Figure 20. Oscilloscope configuration after the tDQSS test                                             |    |

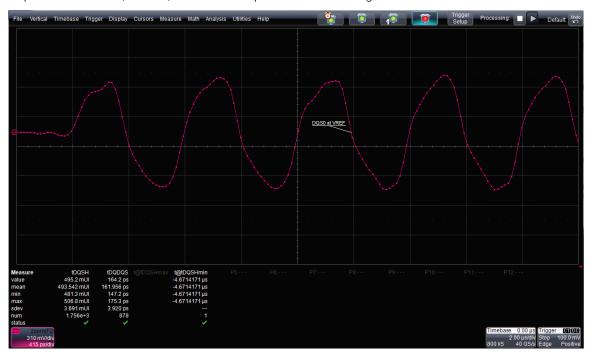

| Figure 21. Oscilloscope configuration after the tDQSH test                                             |    |

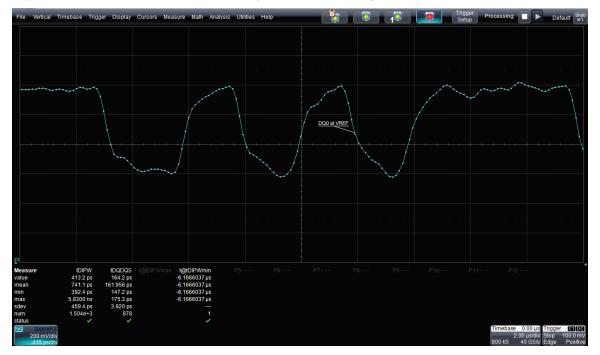

| Figure 22. Oscilloscope configuration after the TdIPW test.                                            | 42 |

| Figure 23. Oscilloscope configuration after the tDSS test.                                             |    |

| Figure 24. Oscilloscope configuration after the tWPST test                                             | 44 |

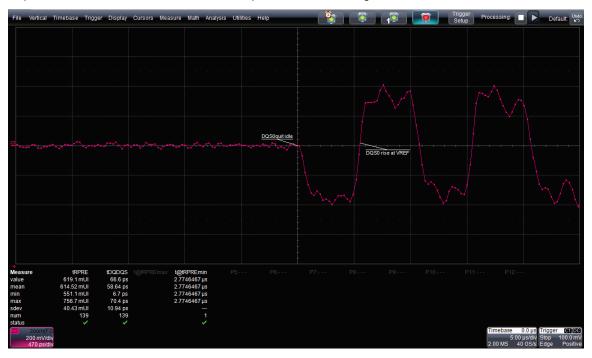

| Figure 25. Oscilloscope tDQSQ test – largest DQS to DQ skew                                            |    |

| Figure 26. Oscilloscope configuration after the tQSH test                                              | 47 |

| Figure 27. Oscilloscope configuration after the tQH_total test.                                        |    |

| Figure 28. Oscilloscope configuration after the tDQSCK test                                            |    |

| Figure 29. Oscilloscope configuration after the tHZ(DQ) test.                                          |    |

| Figure 30. Oscilloscope configuration after the tRPRE test                                             | 52 |

# **About This Manual**

This manual assumes that you are familiar with using an oscilloscope, in particular the Teledyne LeCroy oscilloscope that will be used with QualiPHY and that you have purchased the QPHY-DDR4 software option.

Some of the images in this manual may show QualiPHY products other than QPHY-DDR4, or were captured using different model oscilloscopes, as they are meant to illustrate general concepts only. Rest assured that while the user interface may look different from yours, the functionality is identical.

# Introduction

QualiPHY is highly automated compliance test software meant to help you develop and validate the PHY (physical-electrical) layer of a device, in accordance with the official documents published by the applicable standards organizations and special interest groups (SIGs). You can additionally set custom variables and limits to test compliance to internal standards.

QualiPHY is composed of a "wizard" application that enables the configuration and control of separate tests for each standard through a common user interface. Features include:

- **User-Defined Test Limits** to ensure devices are well within the passing region, even if subsequently measured with different equipment.

- **Flexible Test Results Reporting** that includes XML Test Record generation to better understand device performance distribution or obtain process related information from the devices under test.

QPHY-DDR4 is an automated test package performing all the real-time oscilloscope tests for DDR4 and LPDDR4/4X designs in accordance with JEDEC Standard No. JESD79-4D and JESD209-4-1A. These standards are available from jedec.org.

## **Conventions**

This manual follows these documentation conventions:

- The terms "application" and "software" without any other identifier refer to the QualiPHY DDR4 software option.

- The term "DUT" is an abbreviation for Device Under Test.

- The term "select" is a generic term referring to any method for activating a software control, either using a pointing device or a touch screen.

- The term "Note:" identifies important information.

# **Technical Support**

# **Live Support**

Registered users can contact their local Teledyne LeCroy service center at the number listed on our website. You can also submit Technical Support requests via the website at:

teledynelecroy.com/support/techhelp

#### Resources

Teledyne LeCroy publishes a free Technical Library on its website. Manuals, tutorials, application notes, white papers, and videos are available to help you get the most out of your Teledyne LeCroy products. Visit:

teledynelecroy.com/support/techlib

The Datasheet published on the product page contains the detailed product specifications.

#### **Service Centers**

For a complete list of offices by country, including our sales & distribution partners, visit:

teledynelecroy.com/support/contact

Teledyne LeCroy 700 Chestnut Ridge Road Chestnut Ridge, NY, 10977, USA teledynelecroy.com

#### Sales and Service:

Ph: 800-553-2769 / 845-425-2000 FAX: 845-578-5985 contact.corp@teledynelecroy.com

#### Support:

Ph: 800-553-2769 customersupport@teledynelecroy.com

# Software Installation and Setup

QualiPHY is a Windows-based application that can be configured with one or more serial data compliance components. Each compliance component is purchased as a software option.

# **Oscilloscope Requirements**

#### **Hardware**

The software requires an oscilloscope with at least 13 GHz of bandwidth.

A 13 GHz WaveMaster/SDA 8Zi-B or higher performance oscilloscope is recommended for all speeds of DDR4/LPDDR4/4x testing.

In some cases, at lower memory transfer speeds, 8 GHz bandwidth may be sufficient. Verify the needed slewrates and harmonics will be satisfactory with your chosen oscilloscope bandwidth.

While not required, we recommend for convenience running QualiPHY on an oscilloscope equipped with an additional monitor. This allows the waveforms and measurements to be shown on the oscilloscope display, while the QualiPHY application is displayed on the attached monitor.

See the oscilloscope Operator's Manual for instructions on setting up dual monitor display.

See the DDR4/LPDDR4 Testing section for other required test hardware.

#### **Software**

For the software as shown here, the oscilloscope must be installed with:

- MAUI version 10.5.x.x minimum\* with an activated QPHY-DDR4 option key

- QualiPHY version 10.5.x.x minimum\* with an activated QPHY-DDR4 component

**Note:** The versions listed above are the minimum versions required for the product as shown here. MAUI and QualiPHY software versions must match to the second point, so upgrade your version of QualiPHY if you have upgraded your oscilloscope firmware. The QualiPHY software may be installed on a remote PC, but all other software must be run on the oscilloscope.

• SDAIII, SDAIII-CompleteLinQ, SDA Expert-NRZ or SDA Expert Complete

Note: SDAIII is standard on SDA 8Zi-B model oscilloscopes; you do not need an additional installation.

• Optional, but highly recommended: VirtualProbe software (for fixing reflections, termination, probe points, de-embedding, etc.)

Note: VirtualProbe is included with SDAIII-CompleteLing and SDA Expert Complete.

# **Update Oscilloscope Firmware**

We recommend updating your Windows OS with the latest security patches before installing our software.

Download the latest version of the MAUI firmware from:

teledynelecroy.com/support/softwaredownload/ under Oscilloscope Downloads > Software Utilities

Follow the instructions included with the download to install it.

# **Install QualiPHY Application**

Download the latest version of the QualiPHY software from:

teledynelecrov.com/support/softwaredownload/ under Oscilloscope Downloads > Software Utilities

The application can be installed on either the test oscilloscope or on a remote host computer. For remote execution, see <u>Set Up Remote Control</u>.

If the oscilloscope is not connected to the Internet, copy the installer onto a USB memory stick then transfer it to the oscilloscope desktop or a folder on the D:\ drive to execute it.

Run **QualiPHYInstaller.exe** and follow the installer prompts. Choose all the components you plan to activate. If you omit any components now, you will need to update the installation to activate them later.

By default, the oscilloscope appears as local host when QualiPHY is executed on the oscilloscope. Follow the steps under <u>Add Oscilloscope Connection to QualiPHY</u> to check that the IP address is **127.0.0.1**.

# **Activate QualiPHY Components in MAUI**

The serial data compliance components are factory installed as part of the oscilloscope application (MAUI) and are individually activated through the use of an alphanumeric code uniquely matched to the oscilloscope's serial number. This option key code is what is delivered when purchasing a software option.

To activate a component on the oscilloscope:

- 1. From the menu bar, choose **Utilities > Utilities Setup**.

- 2. On the Options tab, click Add Key.

- Use the Virtual Keyboard to Enter Option Key, then click OK.

If activation is successful, the key code now appears in the list of Installed Option Keys.

- 4. Restart the application by choosing **File > Exit**, then double-clicking the **Start DSO** icon on the desktop.

# **Activate Other Teledyne LeCroy Software**

If newly purchased, activate any other required Teledyne LeCroy software options, such as SDAIII-CompleteLinq. The software is included with the latest firmware, you need only install your option key using the procedure above to activate it.

# **Set Up Remote Control (optional)**

Usually, the oscilloscope is the host computer for the QualiPHY software, and all models that meet the acquisition requirements will also meet the host system requirements. However, the QualiPHY software can be executed from a remote host computer.

To run QualiPHY remotely:

- The oscilloscope must be connected to a LAN and assigned an IP address (fixed or dynamic).

- The host computer must be on the same LAN as the oscilloscope.

## **Remote Host Computer Requirements**

If you wish to run the QualiPHY software from a remote computer, these minimum requirements apply:

- Windows 10 Professional operating system (Windows 11 not currently supported)

- 1 GHz or faster processor

- 1 GB (32-bit) or 2 GB (64-bit) of RAM

- Ethernet (LAN) network capability

- Hard Drive:

- o At least 100 MB free to install the wizard application

- o Up to 2 GB per standard installed to store the log database (each database grows from a few MB to a maximum of 2 GB)

# **Configure Oscilloscope for Remote Control**

- 1. From the oscilloscope menu bar, choose Utilities → Utilities Setup...

- 2. Open the **Remote** tab and set Remote Control to **TCP/IP**.

- 3. Verify that the oscilloscope shows an IP address.

# **Add Oscilloscope Connection to QualiPHY**

- 1. On the host PC, download and run QualiPHYInstaller.exe.

- 2. Start QualiPHY and click the General Setup button.

- 3. On the Connection tab, click Scope Selector.

- 4. Click Add and choose the connection type. Enter the oscilloscope IP address from Step 3 above. Click OK.

- 5. When the oscilloscope is properly detected, it appears on the Scope Selector dialog. Select the connection and click **OK**. QualiPHY is now ready to control the oscilloscope.

# **Select Oscilloscope Connection**

Multiple oscilloscopes may be accessible to a single remote host. In that case, go to the QualiPHY General Setup Connection tab and use the Scope Selector at the start of each session to choose the correct connection.

QualiPHY tests the oscilloscope connection when starting a test. The software warns you if there is a connection problem.

# **Set Up Dual Monitor Display (optional)**

If you are not executing QualiPHY from a remote PC, we recommend attaching a second monitor to the oscilloscope. This allows the waveforms and measurements to be shown on the oscilloscope LCD display while the QualiPHY application and test results are displayed on a second monitor.

See the oscilloscope Operator's Manual for instructions on setting up dual monitor display.

# **Set Up the QualiPHY Application**

The following general settings will persist with each test session you run in QualiPHY. We recommend these be made as part of initial installation. To begin, access the QualiPHY wizard by either:

- Choosing Analysis > QualiPHY from the oscilloscope menu bar

- Double-clicking the QualiPHY desktop icon on a remote computer or oscilloscope desktop.

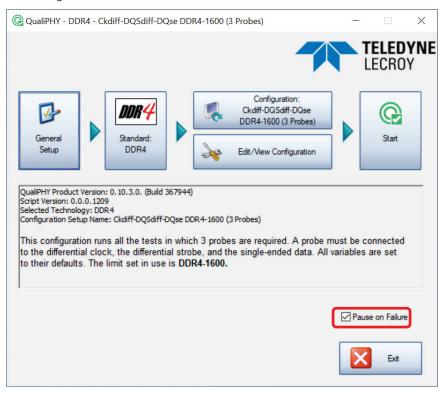

When **Pause on Failure** is checked, QualiPHY will pause execution whenever a test fails and prompt you to make corrections before retrying a measurement. You may open DDR Debug Toolkit to analyze the failure, even if you have not purchased the Debug Toolkit license.

On the Wizard, click the **General Setup** button to continue.

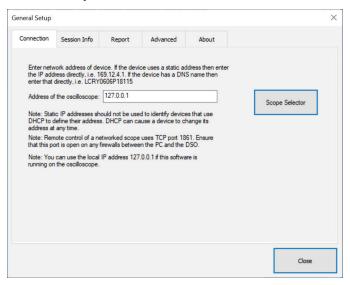

#### **Connection Tab**

The Connection tab shows the **Address of the oscilloscope** is local host 127.0.0.1 when QualiPHY is run from the oscilloscope. If you are running QualiPHY from a remote computer, this will show the network IP address of the oscilloscope to which QualiPHY is currently connected.

The **Scope Selector** button allows you to choose the oscilloscope used for testing when several are connected to the QualiPHY application on a remote host. See Set Up Remote Control for details.

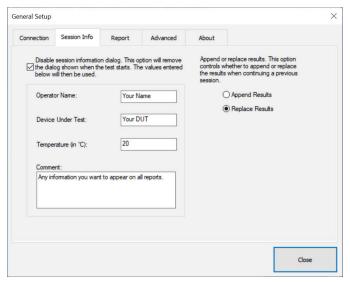

## **Session Info tab**

The Session Info tab contains information that appears on reports, such as: **Operator Name**, **Device Under Test** (DUT) name, **Temperature (in °C)** of the test location, and any additional **Comments**.

If you check **Disable session information dialog**, these global settings will be used on all reports. Otherwise, you will be presented with a dialog at the start of each session that overrides these settings.

There is also a selection to Append Results or Replace Results (overwrite) when continuing a previous test session.

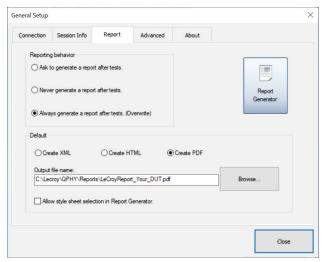

## Report tab

The Report tab contains settings related to report generation.

#### Choose a Reporting behavior of:

- "Ask to generate a report after tests"—you'll be prompted to create a new file for each set of test results.

- "Never generate a report after tests"—you'll need to manually execute the Report Generator.

- "Always generate a report after tests" will autogenerate a report of the latest test results.

Choose a **Default** report output file format of XML, HTML, or PDF.

Optionally, check **Allow style sheet selection in Report Generator** to enable the use of a custom .xslt when generating XML and HTML reports. The path to the .xslt is entered on the Report Generator dialog.

The **Report Generator** button launches the Report Generator dialog, which contains the same settings as the Report tab, only applied to individual reports. This dialog appears automatically at the conclusion of each test group if you have selected "Ask to generate a report after tests."

# DDR4/LPDDR4 Testing

If you are new to QualiPHY, review <u>Using QualiPHY</u> to understand the conventions of the user interface.

# **Required Hardware**

In addition to the oscilloscope, you will need the following to run the DDR4/LPDDR4 tests:

- 3 to 4 DHXX-PB2 Series probes and DH-SI solder tips. This is to measure the DQ (Data), CK (Clock), DQS (Strobe) and possibly the CA (Command Address).

- Interposers make a world of difference in a high-quality setup. They are soldered between the PCB and the DRAM chip to provide easy probing points. Reach out to <a href="Next-sub-rule">Next-sub-rule</a> (world-wide) or <a href="EyeKnowHow">EyeKnowHow</a> (Europe).

- A HDA125 Logic Analyzer is a modular and upgradable MSO that probes the Command Address lanes to trigger and decode. It vastly improves the Read / Write packet separation and is highly recommended.

# **Test Preparation**

Before beginning any test or data acquisition, allow the oscilloscope and probes to warm up for at least 30 minutes after powering on.

Oscilloscope calibration is automatically performed by the oscilloscope application; no manual calibration is required. The calibration procedure will be run again if the temperature of the oscilloscope changes by more than a few degrees.

# **Connecting Probes**

## **Determining Signals to Access**

The required signals to probe depend up on which tests are being run in QPHY-DDR4. The configurations are tailored to different probe setups to allow you to easily see which signals are required for a particular test.

#### **Best Places to Probe**

The DDR4, LPDDR4 and LPDDR4X specifications are defined by the JEDEC standards to be tested at the balls of the DRAM (BGA). The probes should be placed as close to the DRAM as possible in order to follow the JEDEC defined specification. This is important to minimize signal quality issues, such as reflections that can occur on the signals.

For the best signal fidelity capture, it's recommended that an interposer be soldered in between the DRAM and the PCB. Typically, the DRAM sits on the interposer, which sits on a riser board, which sits on the PCB. By using an interposer, the solder-down probe leads can easily be accessed with little impact to the signal.

Two companies that offer interposers and/or installation in circuit are <u>Nexus Technologies</u> (world wide) and <u>EyeKnowHow</u> (Europe).

Another commonly used method is to place vias on the PCB to access the data, strobe, clock or command address signals. These typically are too small, so during layout it's recommended to run traces to make them easier to solder to and place them at similar distances from the BGA. The closer you are to the BGA the better, to help ensure fewer reflections due to trace length. If using this method, apply VirtualProbe software to de-embed the trace lengths with simulated S-parameter files.

## **Deskewing Probes**

For DDR measurements, it is crucial properly deskew probes before running tests to ensure proper signal timing. Ideally, the same settings should be used when deskewing as when acquiring signals for analysis. This will ensure that the channels are deskewed using the same setup as when running compliance tests. Deskew values are saved and stored by QualiPHY at the beginning of each run.

For ease of connectivity, we recommend using the SP tip to deskew, but as long as the same tip is used to deskew each probe, it does not matter which style of tip is used.

## **Required Equipment**

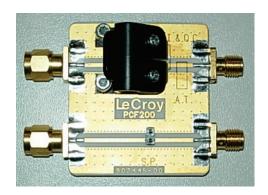

- PCF200 deskew fixture. The fixture has two signal paths:

- The upper path (with the black clip) is for Solder-In (SI), Quick-Link Solder-In (QL-SI), Quick-Connect (QC) and Adjustable Tip (AT) probe tips.

- o The lower path is for Square-Pin (SP) probe tips.

- 50 Ω terminator

Note: Alternatively, use an LPA-K-A adapter and SMA cable.

#### **Deskew Method**

Before beginning the procedure, be sure to warm the oscilloscope for at least 30 minutes.

- 1. Connect the PCF200 to the oscilloscope's fast edge output.

- 2. Connect probes electrically in a single-ended arrangement using their designated area on the fixture:

- Connect the positive side of the probe to the signal trace (in between the two white strips). The positive polarity is indicated on the tip of the probe by a plus sign.

- Connect the negative side to the ground plane (outside of the white strips).

- To minimize reflections, apply a 50  $\Omega$  terminator to the end of the signal path in use. If a 50  $\Omega$  terminator is not available, an SMA cable can be used to terminate the PCF200 to one of the oscilloscope's outputs.

- 3. Set the oscilloscope Trigger Source to Fast Edge, Trigger Type to Edge.

- 4. Set a **Timebase** of approximately **10 ns/div** and **Timebase Delay** of **0**.

Once everything is properly set up, the oscilloscope display should look similar to the figure below. If there is no propagation delay due to the probe, and no internal oscilloscope channel propagation delay, the 50% trigger level will be at the center line of the oscilloscope grid.

- 5. From the channel setup dialog (Cn):

- Enable Sinx/x interpolation and set the Averaging to 50 sweeps.

- Touch the **Deskew** field once to highlight it, then adjust the deskew value to move the rising edge of the trace to the center of the display.

- 6. Now, decrease the **Timebase** to around **20 ps/div** and once again adjust the **Deskew** value so that the 50% rising edge point is centered in time.

Repeat this deskew procedure for each probe using the same probe tip.

Note: Before moving on to the next probe, reset Averaging to 1 sweep and turn off Sinx/x interpolation.

When QualiPHY is started, the deskew values from each channel dialog are saved and stored by QPHY at the beginning of each run. However, at the end of testing these values will be erased. By saving a panel setup (.lss file), it is possible to refer to the deskew values after testing has completed.

# Read (R) and Write (W) Burst Requirements

#### **Read/Write Burst Separation**

One of the most critical aspects of memory testing is separating the bi-directional Data (DQ) and Strobe (DQS) lines, which each have data moving in two directions ("Write" packets from the PHY controller and "Read" packets from the DRAM). If you're testing DDR4 or LPDDR4/4X, there are three different methods for burst separation. Some are more reliable based on the allowable variations of the JEDEC standards.

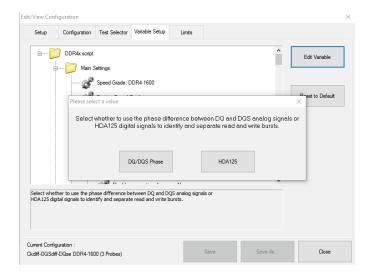

#### **Phase Detection**

In DDR4 we can separate Read and Write bursts depending upon the skew relationship between the Data (DQ) and Strobe (DQS) signals. For a Write burst, the JEDEC standard and the QPHY-DDR4 software expect to see that the DQ and DQS signals are approximately a quarter cycle (~90 degrees) out of phase. For a Read burst, QPHY-DDR4 expects that the DQ and DQS signals are in phase.

#### Preamble Detection

In LPDDR4/4X we can separate the Read and Write bursts depending on a unique set of characteristics of the preamble/postamble relationship of the Data (DQ) and Strobe (DQS). Some designs allow a "don't care" state before the typical idle state of the preamble. For these designs, if there are other signal quality issues, there can be problems separating the burst packets. In that case, use the CMD Address method with the HDA125.

#### Command Address Detection (with HDA125)

For both DDR4 and LPDDR4/4X, the most reliable solution for R/W burst separation is using the HDA125 High-speed Data Analyzer. By probing the Command Address (CA) lines we can determine exactly when the memory is communicating Read or Write information, and the QPHY-DDR4 software uses this for packet separation to overcome any signal quality issues that might cause algorithm challenges.

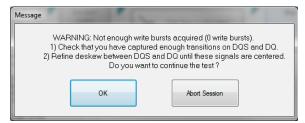

#### **Read/Write Burst Generation**

It is recommended to capture a minimum of 10 Read and 10 Write bursts during each acquisition, but for greater statistical significance, it is encouraged to capture more.

#### DDR4 Burst Generation

Programs that can communicate with the DRAM and controller are widely available. For PCs, one popular option is *Memtest86+*, which is available for download from memtest.org as well is integrated in some PC BIOS menus.

When using Memtest, it is recommended to randomly generate the amount of data. We've found test mode 7, which will randomly generate both Read and Write bursts, to be successful. Other custom programs like *Windows Memory Diagnostic* can be used to stimulate the transfer of data to DIMM.

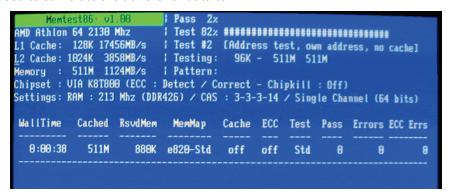

Figure 1. Memtest86+ software.

#### LPDDR4/4X Burst Generation

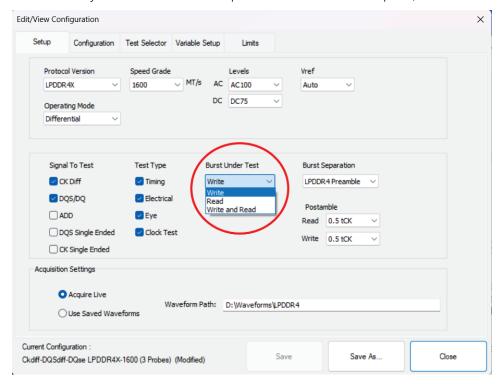

Testing of LPDDR4/4X can be more difficult, as the design is not usually on a PC. Thus, the implementer will typically have a manual way of controlling the DRAM communication in order to generate Read or Write packets. Configure QPHY-DDR4 to analyze either Read or Write packets in the wizard Setup tab, "Burst Under Test".

Figure 2. Choose to analyze Read or Write burst types only.

# **Initial Signal Checking**

Before running QualiPHY to test DDR4, LPDDR4 or LPDDR4X, check the signals to verify that they make sense. This section covers some of the basic things which should be verified by the operator before running QPHY-DDR4.

#### **Expected Channels**

By default, QPHY-DDR4 expects to see the Clock (CK) on CH1, Strobe (DQS) on CH2 and Data (DQ) on CH3. This is what is shown in the connection diagram. The Input Channel variable can always be used to modify any of these channel assignments.

#### **Signal Amplitude Clipping**

For best results, it is recommended that the signals take up 80% of the vertical graticule for the best measurement accuracy. Avoid allowing the signal to go outside the oscilloscope vertical screen, as this clips and removes the usable data.

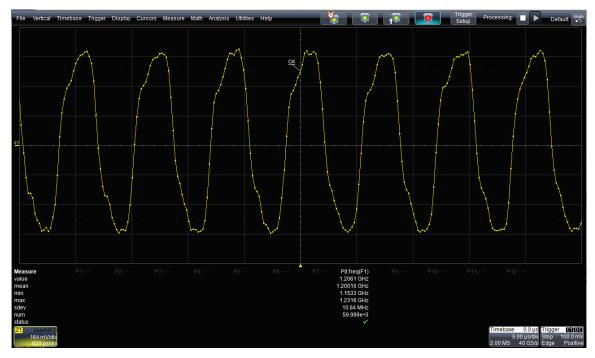

#### **Clock Frequency**

By applying the Frequency measurement parameter to the CK signal, you can verify that the DDR/LPDDR system is running at the expected transfer rate (Transfer Rate = Frequency \* 2). This will also help in the limit selection. Do a quick visual inspection to ensure that the signal does not have any non-monotonic edges due to reflections.

Figure 3. Verification of CK signal.

## **Presence of Read/Write Burst**

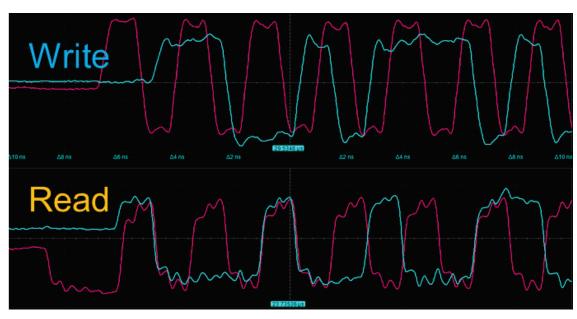

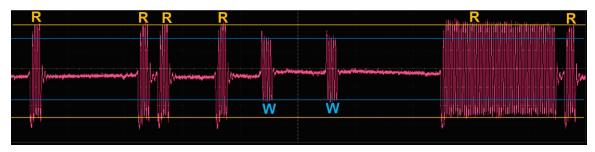

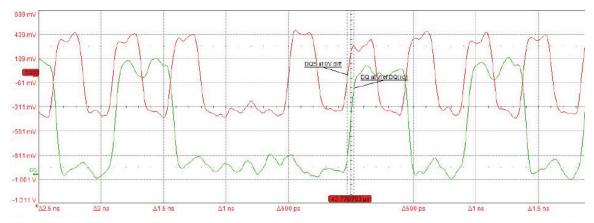

In DDR4, a quick check can evaluate the quality of the burst packets. As a general rule of thumb during a Read burst, DQ and DQS should be in phase, and during a Write burst, DQ and DQS should be a quarter cycle out of phase as seen in Figure 4. Additionally, the signal amplitude can be used to determine the presence of R and Write bursts. If probing at the memory, users can typically expect Read bursts will have a larger amplitude than Write bursts

Figure 4. DDR4 Signal Phase verification (Write out of phase, Read in phase).

Figure 5. Amplitude can help validate if different burst packets are present.

#### **Idle Levels**

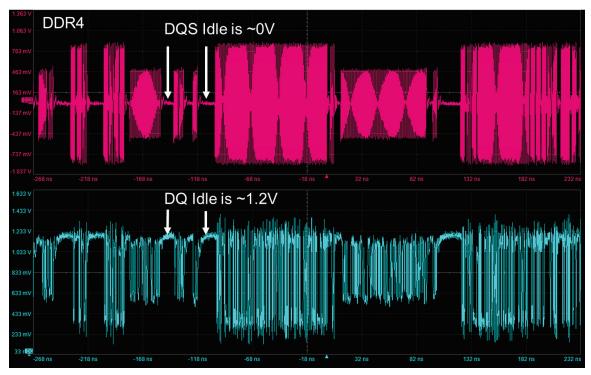

Before running test on DDR4, validate the signal idle levels. Signal idle levels that are off will have an impact on the R/W burst detection, electrical, and timing measurements. DQS should have an idle level of  $\sim 0$  mV. In DDR4, the DQ should have an idle level  $\sim 0$  V to 1.2 V and a DQS  $\sim 0$  V. In LPDDR4/4X this range can be as low as  $\sim 0$  V or can be in a "don't care" state on the DQS. Refer to the JEDEC specification for official requirements.

Figure 6. Verification of Idle levels.

## **Test Initiation**

Follow these steps to begin a new DDR test session in QualiPHY:

- 1. Access QualiPHY by either:

- Choosing Analysis > QualiPHY from the oscilloscope menu bar

- Double-clicking the QualiPHY desktop icon on a remote computer or oscilloscope desktop.

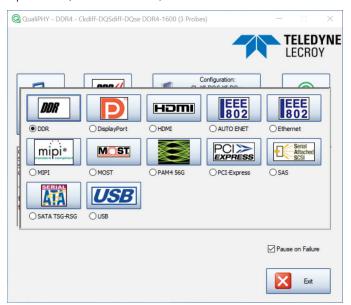

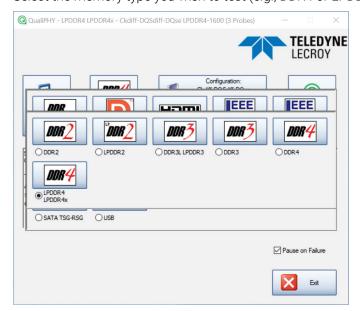

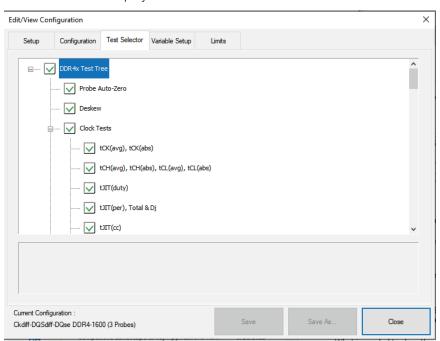

- 2. Open the QualiPHY wizard, select the **Standard** button and choose **DDR**:

3. Select the memory type you wish to test (e.g., DDR4 or LPDDR4 / LPDDR4X).

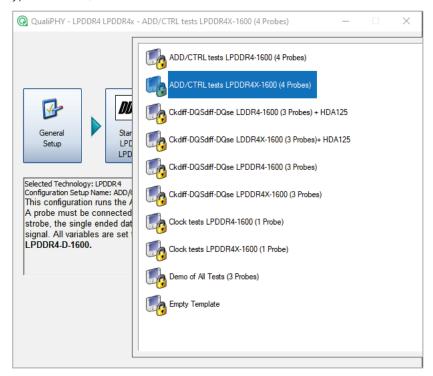

4. On the wizard, click the **Configuration** button and select the test configuration you wish to run. Different configurations are designed to set key variables as required for different probing setups or testing different types of DUTs, etc.

**Note:** Standard configurations are locked and cannot be changed. If you need to change any test variables, you will be prompted to Save As a new copy. See <u>Customizing QualiPHY</u> for more information about creating custom configurations.

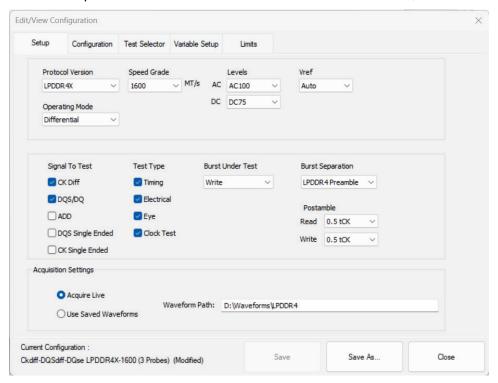

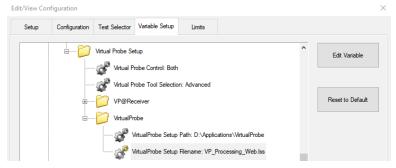

5. Click **Edit/View Configuration** and modify any variables required on the **Setup** tab. The standard configurations are preset to run tests according to JEDEC test standards.

#### For DDR4 testing, set:

- a. Speed Grade: Select the operating memory speed.

- b. Make sure the **Limit Set** matches the Speed Grade. (For example, speed grade 2400 MT/s should match a limit set of DDR4-2400.)

#### For LPDDR4 testing, set:

- a. **Protocol Version**: LPDDR4

- b. Speed Grade: Select the operating memory speed.

- c. Select the Signal(s) to Test (e.g., CK Diff, DQS/DQ, Add or single-ended connections to probes).

- d. Choose the **Test Type(s)** you're interested in running (e.g., Timing, Electrical, Eye, Clock). The individual tests and measurement explanations can be found on the Test Selector tab.

- e. Indicate whether it is the Read or Write Burst Under Test.

- f. Choose a **Burst Separation** method. If using the Preamble method, also enter the number of tCKs in the Read or Write burst **Postamble**. This will help with separation.

- g. Whether to Acquire Live or Used Saved Waveforms. If saved waveforms, enter the Waveform Path.

#### For LPDDR4X testing, set:

- a. **Protocol Version**: LPDDR4X

- b. The output signals of Strobe (DQS) and Clock (CK) of LPDDR4X can operate as single-ended or differential. In SE mode, the DRAM conserves power and uses only the True and not the Compliment portion of the Clock and Strobe. It's important to properly select the **Operating Mode** that represents the memory's output configuration.

- c. **Speed Grade:** Select the operating memory speed. If in Single-Ended Operation Mode, only speeds at or below 1600 MT/s are available.

- d. Select the Signal(s) to Test (e.g., CK Diff, DQS/DQ, Add or single-ended connections to probes).

Note: If in Single Ended Operating Mode, only select Single Ended signals.

- e. Choose the **Test Type(s)** you're interested in running (e.g., Timing, Electrical, Eye, Clock). The individual tests and measurement explanations can be found on the Test Selector tab.

- f. Indicate whether it is the Read or Write Burst Under Test.

- g. Choose a **Burst Separation** method. If using the Preamble method, also enter the number of tCKs in the Read or Write burst **Postamble**. This will help with separation.

- h. Whether to Acquire Live or Used Saved Waveforms. If saved waveforms, enter the Waveform Path.

When done making changes, Save As a new configuration and Close the dialog.

6. Select the new, modified Configuration, then click the **Start** button on the QualiPHY wizard.

7. As configuration diagrams appear, follow the instructions to set up the test equipment.

# DDR4 and LPDDR4/4X Test Configurations

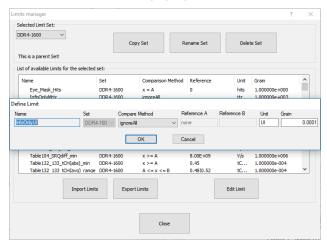

Test configurations include basic test selections, variable settings and limit sets. You may load a test configuration, edit it for the desired speed and setup, then save it for future use. See <a href="DDR4/LPDDR4 Test Descriptions">DDR4/LPDDR4 Test Descriptions</a> and <a href="DDR4/LPDDR4 Variables">DDR4/LPDDR4 Variables</a> and <a href="Limits">Limits</a> for more information about each.

**Note:** The configurations below are customized for DDR4, LPDDR4 or LPDDR4X. For example, the configuration named ADD/CTRL Tests DDR4-1600 (4 Probes) will test at DDR4 limits, while that named ADD/CTRL Tests LPDDR4-1600 (4 Probes) will test at LPDDR4 limits. For the most part, tests are conducted in the same manner, regardless of the standard. Exceptions will be noted in the manual.

Important: Custom configurations will be erased when making a firmware upgrade.

## ADD/CTRL Tests DDR4/LPDDR4/LPDDR4X-1600 (4 Probes)

This configuration runs the Address/Control tests for which four probes are required. A probe must be connected to the differential clock, the differential strobe, the single-ended data, and the single-ended Address/Control signal. All variables are set to their defaults. The limit set in use is DDR4-1600, LPDDR4-1600 or LPDDR4X-1600, depending on which standard you are testing.

## Ckdiff-DQSdiff-DQse DDR4/LPDDR4/LPDDR4X-1600 (3 Probes) + HDA125

This configuration runs all tests for which three probes are required, using the HDA125 for burst separation. A probe must be connected to the differential clock, the differential strobe, and the single-ended data. All variables are set to their defaults. The limit set in use is DDR4-1600, LPDDR4-1600 or LPDDR4X-1600, depending on which standard you are testing.

# Ckdiff-DQSdiff-DQse DDR4/LPDDR4X-1600 (3 Probes)

This configuration runs all tests for which three probes are required, using either Read or Write bursts (as selected in Configuration Setup). A probe must be connected to the differential clock, the differential strobe, and the single-ended data. All variables are set to their defaults. The limit set in use is DDR4-1600, LPDDR4-1600 or LPDDR4X-1600, depending on which standard you are testing.

# Clock Tests DDR4/LPDDR4/LPDDR4X-1600 (1 Probe)

This configuration runs all the clock tests (only) and requires one probe to be connected to the differential clock. All variables are set to their defaults. The limit set in use is DDR4-1600, LPDDR4-1600 or LPDDR4X-1600, depending on which standard you are testing.

# **Demo of All Tests (3 Probes)**

This configuration uses saved waveforms stored in the Waveform Path folder to run the three probe tests. When running normally on the oscilloscope, the path is D:\Waveforms\<standard>. All variables are set to their defaults, except Use Stored Waveforms is set to Yes. The limit set is either DDR4-1600 or LPDDR4-1600, depending on which standard you are testing.

# **Empty Template**

All tests are left deselected to allow creation of a custom configuration. The limit set in use is either DDR4-1600 or LPDDR4-1600, depending on which standard you are testing. All variables are set to their defaults.

# DDR4 and LPDDR4/4X Test Descriptions

These are the DDR4, LPDDR4 and LPDDR4X compliance tests. Unless stated, tests are conducted in the same manner for all three JEDEC memory standards.

## **Probe Auto Zero**

This selection will prompt you to perform an Auto Zero of probes at the beginning of the test session. It should always be performed when changing the probe setup or at the first run after power-up. If Deskew is selected, Auto Zero will be performed during Deskew. It is selected by default for the test configurations; deselected by default for the Demo configuration.

#### Deskew

This selection will guide you step-by-step through the probe deskew process at the beginning of the test session. Deskew should always be performed when changing the probe setup. It is selected by default for the test configurations; deselected by default for the Demo configuration.

#### **Clock Tests**

To add these tests, on the Setup tab, check the box under 'Signal to Test' for *CK Diff* or *CK Single Ended*, then select the "Clock Test" category. This will automatically select the appropriate clock measurements from the Test Selector tab. For a list of explanations, please refer to the measurements below.

## tCK(avg) and tCK(abs)

tCK(avg) is calculated as the average clock period across any consecutive 200 cycle window, where each clock period is calculated from rising edge to rising edge.

tCK(abs) is defined as the absolute clock period, as measured from one rising edge to the next consecutive rising edge.

#### tCH(avg), tCH(abs), tCL(avg) and tCL(abs)

tCH(avg) is defined as the average high pulse width, as calculated across any consecutive 200 high pulses.

tCH(abs) is the absolute instantaneous clock high pulse width, as measured from one rising edge to the following falling edge.

tCL(avg) is defined as the average low pulse width, as calculated across any consecutive 200 low pulses.

tCL(abs) is the absolute instantaneous clock low pulse width, as measured from one falling edge to the following rising edge.

#### tJIT(duty) (DDR4 only)

tJIT(duty) is defined as the cumulative set of tCH jitter and tCL jitter over 200 consecutive cycles.

tCH jitter is the largest deviation of any single tCH from tCH(avg) and tCL jitter is the largest deviation of any single tCL from tCL(avg).

$tJIT(duty) = Min/max \text{ of } \{tJIT(CH), tJIT(CL)\}\$ where,  $tJIT(CH) = \{tCHi - tCH(avg) \text{ where } i=1 \text{ to } 200\} \text{ and } tJIT(CL) = \{tCLi - tCL(avg) \text{ where } i=1 \text{ to } 200\}.$

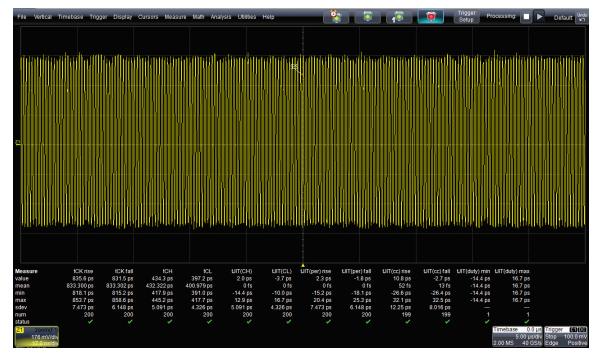

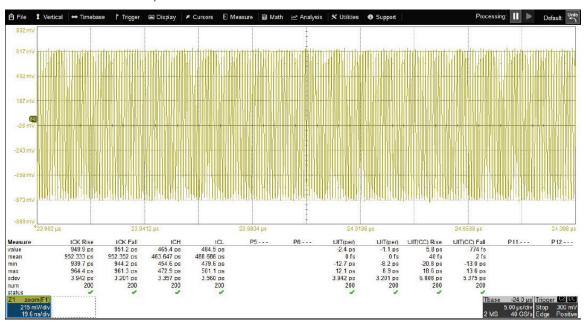

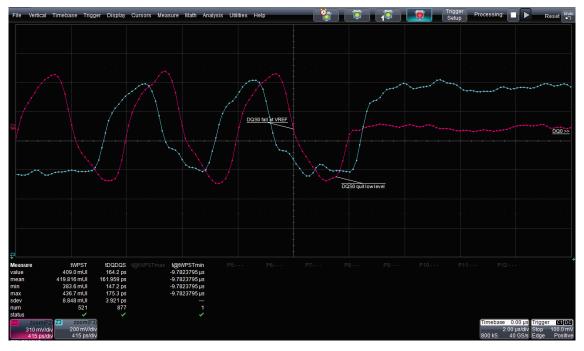

Figure 7. Oscilloscope configuration after tCK, tCH, tCL and tJIT(duty) tests.

Shown on the screen: Z1 is a zoom of the differential clock signal.

#### In the Measure table:

- tCK rise (P1) is the period measurement at Vref (0 mV) of Z1 (differential clock signal) on only the rising edges. The mean value is the measured value for tCK(avg), rise. The minimum value is the measured value for tCK(abs), rise, min reported in mtCK(avg). The maximum value is the measured value for tCK(abs), rise, max reported in mtCK(avg).

- tCK fall (P2) is the period measurement at Vref (0 mV) of Z1 (differential clock signal) on only the falling edges. The mean value is the measured value for tCK(avg), fall. The minimum value is the measured value for tCK(abs), fall, min reported in mtCK(avg). The maximum value is the measured value for tCK(abs), fall, max reported in mtCK(avg).

- tCH (P3) is the width measure at Vref (0 mV) of Z1 (differential clock signal) on only the high pulses. The mean value is the measured value for tCH(avg) reported in mtCK(avg). The minimum value is the measured value for tCH(abs), min reported in mtCK(avg).

- tCL (P4) is the width measure at Vref (0 mV) of Z1 (differential clock signal) on only the low pulses. The mean value is the measured value for tCL(avg) reported in mtCK(avg). The minimum value is the measured value for tCL(abs), min reported in mtCK(avg).

- **tJIT(CH)** (P5) subtracts the mean of P3 (tCH(avg)) from all of the tCH values. The minimum value is the measured value for **tJIT(CH)**, **min** and the maximum value is the measured value for **tJIT(CH)**, **max**.

- tJIT(CL) (P6) subtracts the mean of P4 (tCL(avg)) from all of the tCL values. The minimum value is the measured value for tJIT(CL), min and the maximum value is the measured value for tJIT(CL), max.

- **tJIT(per) rise** (P7) subtracts the mean of P1 (tCK(avg), rise) from all of the tCK rise values. This is displayed for informational purposes only and correlates to the legacy tJIT(per) measurement.

#### DDR4, LPDDR4 and LPDDR4x Compliance Testing Instruction Manual

- **tJIT(per)** fall (P8) subtracts the mean of P2 (tCK(avg), fall) from all of the tCK fall values. This is displayed for informational purposes only and correlates to the legacy tJIT(per) measurement.

- **tJIT(cc)** rise (P9) takes the difference between the clock period of two consecutive cycles for only the rising edge. This is displayed for informational purposes only and correlates to the legacy tJIT(cc) measurement.

- tJIT(cc) fall (P10) takes the difference between the clock period of two consecutive cycles for only the falling edge. This is displayed for informational purposes only and correlates to the legacy tJIT(cc) measurement.

- tJIT(duty) min (P11) is the minimum value of the difference between minimum tCH/tCL clock period and the average tCH/tCL. This is the measured value for tJIT(duty), min in mUI.

- **tJIT(duty) max** (P12) is the maximum value of the difference between minimum tCH/tCL clock period and the average tCH/tCL. This is the measured value for **tJIT(duty)**, **min** in mUI.

## tJIT(per) (DDR4 and LPDDR4/4X) and tJIT(per)\_dj (DDR4 only)

tJIT(per) measures Total jitter (Tj) and in DDR4 the test includes Deterministic jitter (Dj) using the dual-Dirac jitter model, where period measurements constitute the data set for the measurement. Tj and/or Dj are determined at a BER configured.

At the completion of tJIT(per)\_dj (DDR4 only), the oscilloscope displays the following:

Figure 8. Oscilloscope configuration after tJIT(per) and tJIT(per)\_di tests.

Shown on the screen: **RjBUjSpect** is the RjBUj Spectrum of the differential clock signal. The signal type on the signal input section of SDA III is setup to measure a Clock and to use "Period" as the Jitter Parameter.

In the SDA Jitter table:

- Tj(1e-12) is the total jitter calculated using the spectral direct method in SDA III. You can modify the BER level using the *Jitter BER Level* variable (see Jitter BER Level for more information). This value is reported as tJIT(per)\_total in ps for informational purposes. The value is also reported in UI to be tested against the limit from the specification.

- **Rj(spD)** is the random jitter calculated using the spectral direct method in SDA III. This value is reported for informational purposes.

- **Dj(spD)** is the deterministic jitter calculated using the spectral direct method in SDA III. This value is reported as **tJIT(per)\_dj** in ps for informational purposes. The value is also reported in UI to be tested against the limit from the specification.

## tJIT(cc)

This test measures Total jitter (Tj) using the dual-Dirac jitter model, where cycle-to-cycle measurements constitute the data set for the measurement. Tj is determined at a BER configured.

At the completion of the tJIT(cc) test, the oscilloscope shows the following (slight differences between DDR4 and LPDDR4/4X measurement results):

Figure 9. Oscilloscope configuration after tJIT(cc) tests.

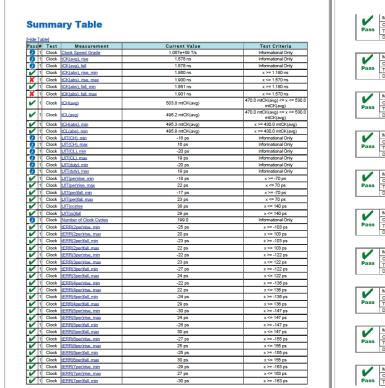

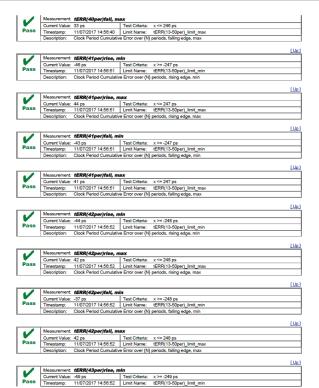

#### tERR(nper) (DDR4 only)

tERR(nper) is defined as the cumulative error across n multiple clock cycles from tCK(avg). This test is performed with n ranging from 2 to 50 clock periods.

There are 12 different tests: tERR(2per), tERR (3per), tERR (4per), tERR (5per), tERR (6per), tERR (7per), tERR (8per), tERR (12per), tERR (12per), tERR (12per), tERR (13-50per).

Note: Only tERR(2per), tERR (3per), tERR (4per), and tERR (5per) will be discussed below. The setup for all tERR(n per) tests is exactly the same.

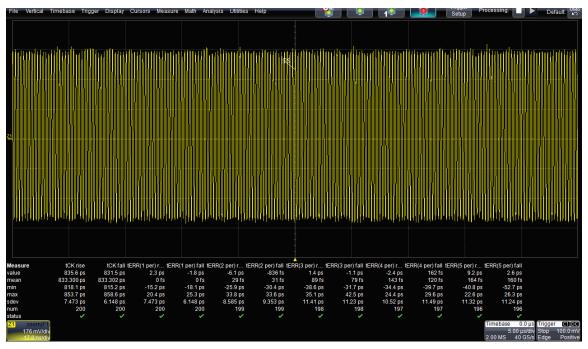

At the completion of the tERR(2per), tERR (3per), tERR (4per), and tERR (5per) tests, the oscilloscope is in the following state:

Figure 10. Oscilloscope configuration after tERR(2per), tERR (3per), tERR (4per) and tERR (5per) tests.

Shown on the screen: Z1 is a zoom of the differential clock signal.

In the Measure table:

- tCK rise (P1) is the period measurement at Vref (0 mV) of Z1 (differential clock signal) on only the rising edges. This value is used for the tERR calculation on the rising edge.

- tCK fall (P2) is the period measurement at Vref (0 mV) of Z1 (differential clock signal) on only the falling edges. This value is used for the tERR calculation on the rising edge.

- **tERR(1 per) r** (P3) is the TIE measure at Vref (0 mV) of Z1 (differential clock signal) on only the rising edges (positive pulses). It is set up to measure edges at intervals of 1. This is reported as informational only.

- **tERR(1 per) fall** (P4) is the TIE measure at Vref (0 mV) of Z1 (differential clock signal) on only the falling edges (negative pulses). It is set up to measure edges at intervals of 1. This is reported for information only.

- **tERR(2 per) r** (P5) is the TIE measure at Vref (0 mV) of Z1 (differential clock signal) on only the rising edges (positive pulses). It is set up to measure edges at intervals of 2. The minimum value is measured as **tERR(2per)rise, min** reported in mUI and the maximum value is measured as **tERR(2per)rise, max** reported in mUI.

- tERR(2 per) fall (P6) is the TIE measure at Vref (0 mV) of Z1 (differential clock signal) on only the falling edges (negative pulses). It is set up to measure edges at intervals of 2. The minimum value is measured as tERR(2per)fall, min reported in mUI and the maximum value is measured as tERR(2per)fall, max reported in mUI.

- **tERR(3 per) r** (P7) is the TIE measure at Vref (0 mV) of Z1 (differential clock signal) on only the rising edges (positive pulses). It is set up to measure edges at intervals of 3. The minimum value is measured as **tERR(3per)rise, min** reported in mUI and the maximum value is measured as **tERR(3per)rise, max** reported in mUI.

- tERR(3 per) fall (P8) is the TIE measure at Vref (0 mV) of Z1 (differential clock signal) on only the falling edges (negative pulses). It is set up to measure edges at intervals of 3. The minimum value is measured as tERR(3per)fall, min reported in mUI and the maximum value is measured as tERR(3per)fall, max reported in mUI.

- tERR(4 per) r (P9) is the TIE measure at Vref (0 mV) of Z1 (differential clock signal) on only the rising edges (positive pulses). It is set up to measure edges at intervals of 4. The minimum value is measured as tERR(4per)rise, min reported in mUI and the maximum value is measured as tERR(4per)rise, max reported in mUI.

- tERR(4 per) fall (P10) is the TIE measure at Vref (0 mV) of Z1 (differential clock signal) on only the falling edges (negative pulses). It is set up to measure edges at intervals of 4. The minimum value is measured as tERR(4per)fall, min reported in mUI and the maximum value is measured as tERR(4per)fall, max reported in mUI.

- tERR(5 per) r (P11) is the TIE measure at Vref (0 mV) of Z1 (differential clock signal) on only the rising edges (positive pulses). It is set up to measure edges at intervals of 5. The minimum value is measured as tERR(5per)rise, min reported in mUI and the maximum value is measured as tERR(5per)rise, max reported in mUI.

- tERR(5 per) fall (P12) is the TIE measure at Vref (0 mV) of Z1 (differential clock signal) on only the falling edges (negative pulses). It is set up to measure edges at intervals of 5. The minimum value is measured as tERR(5per)fall, min reported in mUI and the maximum value is measured as tERR(5per)fall, max reported in mUI.

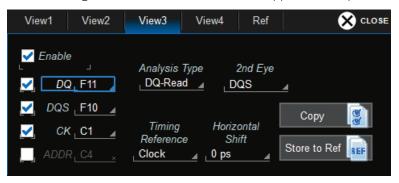

# **Eye Diagram Tests on Write Bursts**

## DQ and DQS Eye

This is an informational only test that creates an eye diagram for DQ and DQS of all the Write bursts detected in the acquisition. DQS is the timing reference for both eye diagrams and the reference point is shown on the center screen.

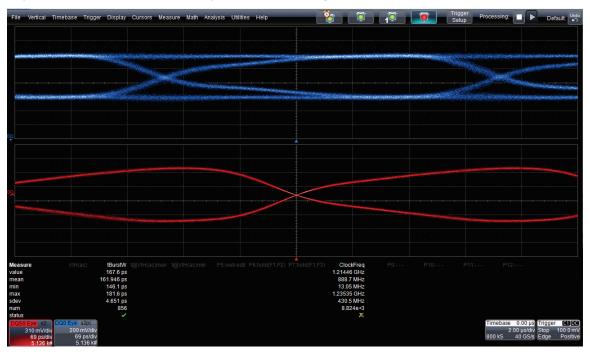

At the completion of the test, the oscilloscope is in the following state:

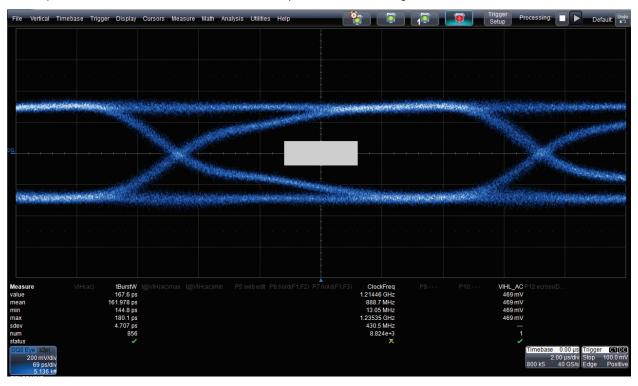

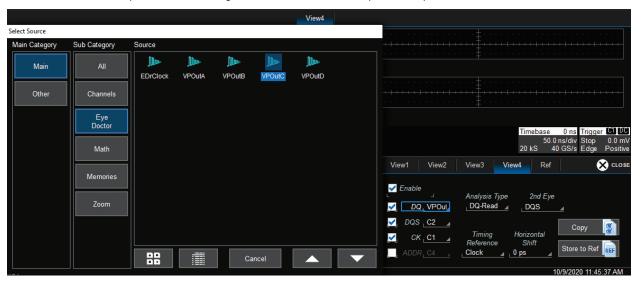

Figure 11. Oscilloscope configuration after Write Bursts (Inputs) - DQ and DQS Eyes.

#### Shown on the screen:

- F6 is the **DQS Eye** diagram of the write bursts from the acquired signal. DQS is used as the timing reference for this test which causes the eye to come to a "pin point" on the center grid. This math function is assigned an alias based on the assigned DQS signal name. The number of bits contained in the eye diagram is displayed in the bottom row of the F6 descriptor box. In this case there are 5,136 DQS bits in the eye.

- F7 is the **DQ Eye** diagram of the write bursts from the acquired signal. This math function is assigned an alias based on the assigned DQ signal name. The number of bits contained in the eye diagram is displayed in the bottom row of the F7 descriptor box. In this case there are 5,136 DQ bits in the eye.

#### In the Measure table:

- tBurst W (P2) displays the number of Write bursts detected in the acquisition.

- ClockFreq (P8) is the measured clock frequency from the acquired waveform.

## **DQ Write Input Compliance Mask**

This tests the DQ Write Eye against the mask defined in the specification. The mask is created from the TdIVW\_total and VdIVW\_total limits for different speeds.

At the completion of the DQ Input Compliance Mask test, the oscilloscope is in the following state:

Figure 12. Oscilloscope configuration after DQ Write Input Compliance Mask test.

#### VIHL\_AC

VIHL\_AC will test the peak-to-peak amplitude of the DQ signal for each UI. The DQ signal must meet or exceed the specified level at any point over the total UI. It is measured as a peak-to-peak voltage centered at Vref.

At the completion of the VIHL\_AC test, the oscilloscope is in the following state:

Figure 13. Oscilloscope configuration after VIHL\_AC test.

Shown on the screen: F7 is the **DQ** Eye diagram of the Write bursts from the acquired signal. The DQS signal is the timing reference for this eye diagram. This math function is assigned an alias based on the assigned DQ signal name. The number of bits contained in the eye diagram is displayed in the bottom row of the F7 descriptor box. In this case there are 5,136 DQ bits in the eye.

In the Measure table:

- **tBurst W** (P2) displays the number of Write bursts detected in the acquisition.

- **ClockFreq** (P8) is the measured clock frequency from the acquired waveform.

- VIHL\_AC (P11) calculates the minimum eye opening for each UI. The measured value is reported as VIHL\_AC min.

#### tDQS2DQ (DDR4)

tDQS2DQ will measure the timing offset in Unit Intervals (DDR4) or pico-seconds (LPDDR4/4X) of the Rx Mask that is set up. This is the DQS\_t DQS\_c crossing in reference to the position of the DQ Rx Mask center position. There is an allowable range given by the JEDEC that is tested against to validate the timing offset is within the correct range.

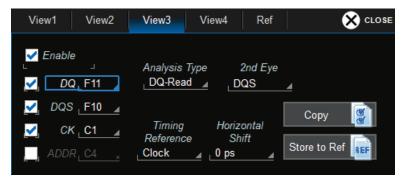

## **Eye Diagram Tests on Read Bursts**

#### DQ and DQS Eye

This is an informational test that creates an eye diagram for DQ and DQS of all of the Read bursts detected in the acquisition. DQS is the timing reference for both eyes and the reference point is shown on the second division.

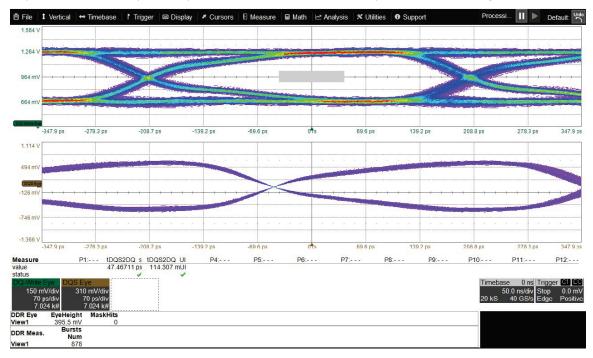

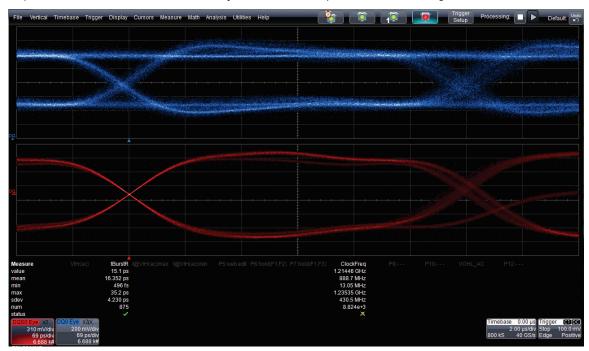

At the completion of Read Bursts: DQ & DQS Eye, the oscilloscope is in the following state:

Figure 14. Oscilloscope configuration after Read Bursts (Outputs) test.

#### Shown on the screen:

- F6 is the **DQS** Eye diagram of Read bursts from the acquired signal. DQS is used as the timing reference for this test which causes the eye to come to a "pin point" on the second division. This math function is assigned an alias based on the assigned DQS signal name. The number of bits contained in the eye diagram is displayed in the bottom row of the F6 descriptor box. Here there are 7,000 DQS bits in the eye.

- F7 is the **DQ Eye** diagram of Read bursts from the acquired signal. This math function is assigned an alias based on the assigned DQ signal name. The number of bits contained in the eye diagram is displayed in the bottom row of the F7 descriptor box. Here there are 7,000 DQ bits in the eye.

#### In the Measure table:

- tBurst R (P2) displays the number of Read bursts detected in the acquisition.

- ClockFreq (P8) is the measured clock frequency from the acquired waveform.

## tQW\_total (LPDDR4/4X only)

tQW\_total is a measurement that occurs on window time (think of it as the DQ Eye diagram width) of the read packet, which is the output data of the DRAM to the controller. This occurs at a selected DQx pin and is also defined by the JEDEC as when the Data Bus Inversion (DBI) is disabled.

# Eye Diagram Tests on CA/CS (LPDDR4/4X only)

Analysis on the Command Address (CA) or Chip Select (CS) lines is important for signal quality inspection. Testing one or more signal lines is preferred, but the shortest and longest trace lengths will typically give you a good approximation.

#### **CA/CS Eye**

This is an informational only test that creates an eye diagram for CA or CS signals of all the Write bursts (input signals) detected in the acquisition. Vcent\_CA is the timing reference for these eye diagrams.

#### **CA/CS Mask**

The test verifies no signal from the eye diagram goes through the JEDEC defined mask. The parameters for the mask are created from the TdIVW and VdIVW limits that change based on the designated DQ signal speed.

#### VIHL\_AC for CA/CS

VIHL\_AC will test the peak-to-peak amplitude of the CA or CS signal for each UI. The signal must meet or exceed the specified level at any point over the total UI. It is measured as a peak-to-peak voltage centered at Vcent\_CA or Vcent\_CS.

# tDVAC (DDR4 only)

The purpose of this test is to verify the allowed time before ringback for the differential CK signal. It is measured as the time above the VIH(ac) level and below the VIL(ac) level. The clock signal is only measured when a Write burst has been detected.

**Note:** Only tDVAC measured on above VIH(ac) will be discussed below. The measurement methodology is exactly same for below VIL(ac).

At the completion of the tDVAC test, the oscilloscope is in the following state:

Figure 15. Oscilloscope configuration after the tDVAC test.

Shown on the screen: **Z1** is a zoom of F1, the acquired CK signal after any probe deskew has been applied. The zoom is positioned at the location of the "worst case" tDVAC measurement indicated by t@tVACmin. A label is applied to this trace according to the signal name assigned to CK and placed at the VIH(ac) level.

- tVACvih (P1) is measuring the time above VIH(ac) for CK. VIH(ac) is indicated by the trace label "CK at VIH(ac)". The minimum value is the measured value for tDVAC min of CK. Because the limit is undefined by the specification, this test is Informational only.

- **tDQDQS** (P2) is measuring the skew between DQ and DQS. Since this measurement is performed once per burst, this shows how many Write bursts were in the acquired waveform.

- **t@tVACmin** (P4) displays the location of where the minimum value of tDVAC occurred. This is used to position the zoom traces at the location of the "worst case results".

- Slew(z1) is measuring the slewrate on the rising edge of CK at t@tVACmin from Vref to VIH(ac). This value is used to determine the appropriate limit for tDVAC.

# **Electrical Tests on Write Bursts (Inputs)**

### **Input Slewrate**

The purpose of these tests is to characterize the slewrate on all the Write (input) signals. The tests are performed on both rising and falling edges. By default the slewrate is measured on different signal types (DQ, DQS, CK, CA) depending on the measurement standard and their defined thresholds.

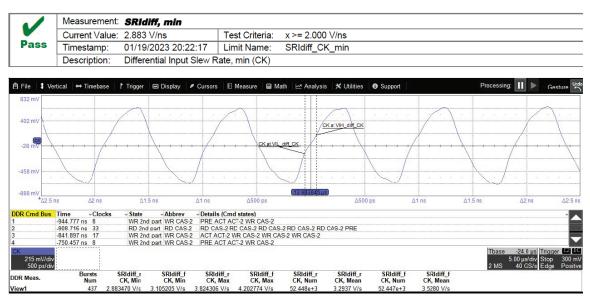

### SRIdiff (DQS and CK)

For DDR4, the input slewrate is measured only on DQS. It's measured on each Input packet using the reference level of VIHdiff to VILdiff that is defined by the JEDEC per speed.

For LPDDR4/4X, the input slewrate is measured on DQS and CK. It's measured on each Input packet using the reference level of VIHdiff to VILdiff that is defined by the JEDEC per speed.

The QualiPHY report will show the result of the slewrate measured between the VILdiff and VIHdiff locations. The result will also show a separate min/max value that is tested to the JEDEC's limit. Results are in volts per nanoseconds (V/ns).

Figure 16. Oscilloscope configuration after SRIdiff\_CK test.

### srr1 and srf1 (DDR4 only)

This test measures the slewrate on DQ for rising and falling edges during Write bursts. The srr1 and srf1 are measuring the slew by dividing the voltage VDIVW(max) (speed-grade dependent) by the time found to traverse Vref.DQ(Write) +/- 0.5 \* VDIVW(max). Both minimum and maximum values are measured for srr1 and srf1.

### srr2 and srf2 (DDR4 only)

This test measures the slewrate on DQ for rising and falling edges during Write bursts above and below the mask voltage. Both minimum and maximum values are measured for srr2 and srf2.

srr2 = (VIHL\_AC(min) - VdIVW(max)) / (2\*tr2)

srf2 = (VIHL\_AC(min) - VdIVW(max)) / (2\*tf2)

### SRIN\_dIVW and SRIN\_cIVW (LPDDR4/4X only)

These tests measure the Input Slewrate Rise and Fall over the VdiVW\_total for the DQ and CA signals. Being based on the VdiVQ means that the high and low level of the Rx Mask (height) will define the upper and lower thresholds for the slewrate in reference to the center at either Vcent\_DQ or Vcent\_CA.

Figure 17. Oscilloscope configuration after SRIN\_diVW, max test.

#### AC Over/Undershoot Peak and Area

The purpose of this test group is to characterize the overshoot above VDDQ and undershoot below VSSQ on DQ, DQS, CK and CA/ADDR during Write bursts. Both peak amplitude and area are tested.

**Note:** Only DQ overshoot will be shown here. The measurement methodology is exactly same for the DQS, CK, and CA/ADDR. The measurement methodology is also identical for undershoot and overshoot, except that VSSQ is used for undershoot instead of VDDQ.

#### DQ

This test measures the overshoot/undershoot, peak and area measurements on DQ signals:

- VDOSP: Maximum peak amplitude above VDOS

- VDUSP: Maximum peak amplitude below VDUS

- ADOS1: Maximum overshoot area per 1 UI between VDDQ and VDOS

- ADOS2: Maximum overshoot area per 1 UI above VDOS

- ADUS1: Maximum undershoot area per 1 UI between VSSQ and VDUS1

- ADUS2: Maximum undershoot area per 1 UI below VDUS

At the completion of the DQ Peak Amplitude test, the oscilloscope is in the following state:

Figure 18. Oscilloscope configuration after Overshoot Peak Amplitude test.

#### Shown on the screen:

- **Z2** is a zoom of F2, the acquired DQS signal after any probe deskew has been applied. The zoom is positioned at the location of the "worst case" Overshoot Peak Amplitude measurement indicated by t@PeakMax. This signal is not measured in this test and is only provided as a visual reference.

- **Z3** is a zoom of F3, the acquired DQ signal after any probe deskew has been applied. The zoom is position at the location of the "worst case" Overshoot Peak Amplitude measurement indicated by t@PeakMax. A trace label is applied on the pulse with the worst overshoot peak amplitude. This is the signal which is measured in this test.

- OvershootPeak (P1) is measuring the overshoot peak amplitude above VDDQ for of each DQ pulse. The

VDDQ level is indicated by alternating dashed cursor and the peak amplitude level is indicator by the other

cursor. The peak amplitude is measured only 1 UI after a transition. If the peak value does not exceed VDDQ

the measured value will return a negative result. The maximum value is the measured value for DQ

Overshoot peak amplitude Max. This test is considered passing if the measured value is less than 400 mV.

- **t@PeakMax** (P3) displays the location of where the maximum value of OvershootPeak occurred. This is used to position the zoom traces at the location of the "worst case results".

#### DOS

This test measures the overshoot/undershoot, peak and area measurements on single-ended DQS\_t and DQS\_c signals, using the methodology described above:

- VDOSP: Maximum peak amplitude above VDOS

- VDUSP: Maximum peak amplitude below VDUS

- ADOS1: Maximum overshoot area per 1 UI between VDDQ and VDOS

- ADOS2: Maximum overshoot area per 1 UI above VDOS

- ADUS1: Maximum undershoot area per 1 UI between VSSQ and VDUS1

- ADUS2: Maximum undershoot area per 1 UI below VDUS

#### CK

This test measures the overshoot/undershoot, peak and area measurements on single-ended CK\_t and CK\_c signals, using the methodology described above:

- VCOSP: Maximum peak amplitude above VCOS

- VCUS: Maximum peak amplitude allowed for undershoot

- ACOS1: Maximum overshoot area per 1 UI between VDD and VDOS

- ACOS2: Maximum overshoot area per 1 UI above VCOS

- ACUS: Maximum undershoot area per 1 UI below VSS

#### CA/ADDR

This test measures the overshoot/undershoot, peak and area measurements on single-ended Command and Address signals, using the methodology described above:

- VAOSP: Maximum peak amplitude above VAOS

- VAUS: Maximum peak amplitude allowed for undershoot

- AAOS1: Maximum overshoot area per 1 tCK between VDD and VAOS

- AAOS2: Maximum overshoot area per 1 tCK above VDOS

- AAUS: Maximum undershoot area per 1 tCK below VSS

## Differential Amplitude and Levels: Vindiff, VIHdiff, VILdiff (LPDDR4 only)

#### Vindiff (CK or DQS)

The minimum differential voltage input (peak to peak) needed to satisfy the JEDEC requirement for input receiver voltage is measured as Vindiff. The JEDEC specification sets out minimum pk-pk voltage ranges based on the signal's data rate and type. A (Max Peak Voltage – Minimum Peak Voltage) is performed and reported against all test pulses, and if any differential signal is below the accepted limit, the test is reported as a failure.

#### VIHdiff (CK or DQS)

The differential input voltage for the CK or DQS is defined as the High point. This value is measured to the JEDEC standard and used for making differential slewrate measurements.

#### VILdiff (CK or DQS)

The differential input voltage for the CK or DQS is defined as the Low point. This value is measured to the JEDEC standard and used for making differential slewrate measurements.

### Single-ended Tests: Vinse

The Voltage Input Single-Ended test measures both the high limit and low limit in reference to the VrefDQ level.

### CK\_t, CK\_c (DDR4 and LPDDR4/4X)

This measurement of the signal amplitude confirms no packets of the Clock (CK\_t or CK\_c) are outside their JEDEC defined limits.

### DQS\_t, DQS\_c (LPDDR4/4X only)

This measurement of the signal amplitude confirms no packets of the Strobe (DQS\_t or DQS\_c) are outside their JEDEC defined limits.

## **Electrical Tests on Read Bursts (Outputs)**

### **Output Slewrate**

The purpose of these tests is to characterize the slewrate on DQ and DQS of all the Read bursts (output) in the acquisition. This test is performed on the Slewrate (SR) of the Query Output (Q) for both Single-ended (SE) and Differential (diff) setups (ie SRQse and SRQdiff). The rising and falling edges are measured against the minimum and maximum values allowed by the JEDEC standard for its corresponding speed.

**Note:** Only slewrate measured on the rising edge of DQ is shown below. The measurement methodology is exactly same for the falling edge, except the slewrate is measured from VOH(ac) to VOL(ac) instead of VOL(ac) to VOH(ac). The measurement methodology is also identical for DQS.

#### **SRQse**

This test measures the slewrate of the single ended DQ output signals during Read bursts. Slew is measured between VOH(AC) and VOL(AC). Both the max and min values are measured.

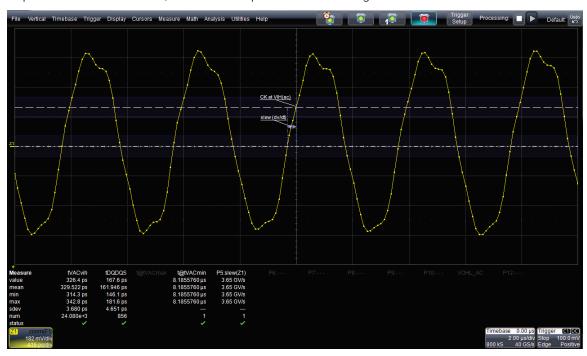

At the completion of the SRQse test, the oscilloscope is in the following state:

Figure 19. Oscilloscope configuration after the SRQ test.

#### Shown on the screen:

- **Z2** is a zoom of F2, the acquired DQS signal after any probe deskew has been applied. The zoom is positioned at the location of the "worst case" SRQ R measurement indicated by t@SRQ Rmin. This signal is not measured and is only provided as a visual reference.

- **Z3** is a zoom of F3, the acquired DQ signal after any probe deskew has been applied. The zoom is position at the location of the "worst case" SRQ R measurement indicated by t@SRQ Rmin. This is the signal that is measured in this test.

#### In the Measure table:

- SRQ R (P1) is measuring the slewrate of DQ on the rising edges. The slewrate on the rising edge is measured from VOL(ac) to VOH(ac). The minimum value is the measured value for SRQ R of DQ min. This test is passed if the measured value is greater than 4 GV/s.

- **tDQDQS** (P2) is measuring the skew between DQ and DQS. Since this measurement is performed once per burst, this shows how many Read bursts were in the acquired waveform.

- t@SRQ Rmin (P4) displays the location of where the minimum value of SRQ R occurred. This is used to position the zoom traces at the location of the "worst case results".

- **P5:** slew(Z3) displays the minimum value of SRQ R and is used to display the slewrate measurement markers.

### R/F Ratio (LPDDR4 only)

This test measures the Output slew-rate matching Ratio (Rise to Fall) for single-ended signals, as defined by the JEDEC standard. The reference levels are the VOL(AC) = 0.2\*VOH(DC) and VOH(AC) = 0.8\*VOH(DC).

### **SRQdiff**

This test measures the slewrate of the differential DQS output signals during Read bursts. Slew is measured between VOH.Diff(AC) and VOL.Diff(AC). Both the max and min values are measured.

## **Timing Tests on Write Bursts**

### Timing Tests on Bits (not using interpolation)

### tDQSS (DDR4 only)

This test characterizes the allowed range for a rising DQS edge relative to CK on Write bursts. This measures the time from CK rising at Vref to the nearest DQS rising at Vref. Both the maximum and minimum values are measured. This test is very similar to tDQSCK, which is measured on Read bursts.

At the completion of the tDQSS test, the oscilloscope is in the following state:

Figure 20. Oscilloscope configuration after the tDQSS test.

#### Shown on the screen:

- Z1 is a zoom of F1, the acquired CK signal after any probe deskew has been applied. The zoom is position at the location of the "worst case" tDQSS measurement indicated by t@tDQSSmax. A trace label is applied on this trace at Vref.

- **Z2** is a zoom of F2, the acquired DQS signal after any probe deskew has been applied. The zoom is positioned at the location of the "worst case" tDQSS measurement indicated by t@tDQSSmax. A trace label is applied at Vref on this trace according to the signal name assigned to DQS.

- tDQSS (P1) is measuring the skew between CK and DQS. The skew is measured between CK rising at Vref to the nearest DQS rising at Vref. Essentially the time between the two trace labels is measured. The maximum value is the measured value for tDQSS max and is reported in mtCK(avg). This test is considered informational only since the limit is undefined.

- **tDQDQS** (P2) is measuring the skew between DQ and DQS. Since this measurement is performed once per burst, this shows how many Write bursts were in the acquired waveform.

- t@tDQSSmax (P3) displays the location of where the maximum value of tDQSS occurred. This is used to position the zoom traces at the location of the "worst case results".

#### tDQSH and tDQSL

These tests measure the high (tDQSH) and low (tDQSL) pulse widths of each DQS signal during a W burst. Both the maximum and minimum tDQSH/tDQSL values are measured. This tests are very similar to tQSH and tQSL, which are measured on Read bursts.

**Note:** Only tDQSH will be discussed below. The measurement methodology is the same for the tDQSL expect the measurement is made on DQS from falling edge to a rising edge instead of a rising edge to a falling edge.

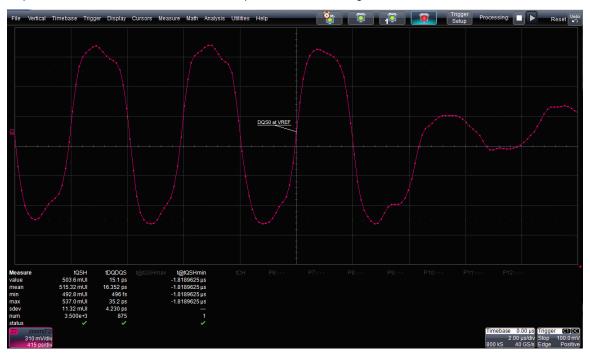

At the completion of the tDQSH test, the oscilloscope is in the following state:

Figure 21. Oscilloscope configuration after the tDQSH test.

Shown on the screen: **Z2** is a zoom of F2, the acquired DQS signal after any probe deskew has been applied. The zoom is positioned at the location of the "worst case" tDQSH measurement indicated by t@tDQSHmin. A trace label is applied at Vref on this trace according to the signal name assigned to DQS.

- **tDQSH** (P1) is measuring the high time of DQS. The high time is determined by measuring the time DQS crosses Vref on a rising edge at to the time DQS crosses the next associated falling edge at Vref. The minimum value is the measured value for **tDQSH min** and is reported in mtCK(avg). This test is considered informational only since the limit is undefined.

- **tDQDQS** (P2) is measuring the skew between DQ and DQS. Since this measurement is performed once per burst, this shows how many Write bursts were in the acquired waveform.

- **t@tDQSHmin** (P4) displays the location of where the minimum value of tDQSH occurred. This is used to position the zoom traces at the location of the "worst case results".

#### **TdIPW**

This test measures the pulse widths of the DQ signal during the Write burst. The minimum value is measured on both high and low pulses.

At the completion of the TdIPW test, the oscilloscope is in the following state:

Figure 22. Oscilloscope configuration after the TdIPW test.

#### Shown on the screen:

• **Z3** is a zoom of F3, the acquired DQ signal after any probe deskew has been applied. The zoom is positioned at the location of the "worst case" tDIPW measurement indicated by t@tDIPWmin. A trace label is applied at Vref on this trace according to the signal name assigned to DQ.

- TdIPW (P1) is the high time of DQS. The high time is determined by measuring the time DQ crosses Vref on a rising edge (centered on the screen) at to the time DQ crosses the next associated falling edge at Vref (indicated by the trace label). The minimum value is the measured value for TdIPW min High and is reported in mUI. This test is considered passing if the minimum value is greater than 0.58 UI.

- **tDQDQS** (P2) is the skew between DQ and DQS. Since this measurement is performed once per burst, this shows how many Write bursts were in the acquired waveform.

- **t@tDIPWmin** (P4) displays the location of where the minimum value of TdIPW occurred. This is used to position the zoom traces at the location of the "worst case results".

#### tDSS and tDSH

These tests characterize the setup and hold time for a falling DQS edge to the rising CK edge on Write bursts. The minimum value is measured for both tDSS and tDSH.

**Note:** Only tDSS will be discussed below. The measurement methodology is the same for the tDSH expect the hold time is measured rather than the setup time.

At the completion of the tDSS test, the oscilloscope is in the following state:

Figure 23. Oscilloscope configuration after the tDSS test.

#### Shown on the screen:

- **Z1** is a zoom of F1, the acquired CK signal after any probe deskew has been applied. The zoom is position at the location of the "worst case" tDSS measurement indicated by t@tDSSmax. A trace label is applied on this trace at Vref.

- **Z2** is a zoom of F2, the acquired DQS signal after any probe deskew has been applied. The zoom is positioned at the location of the "worst case" tDSS measurement indicated by t@tDSSmax. A trace label is applied at Vref on this trace according to the signal name assigned to DQS.

- tDSS (P1) is measuring the setup time from when the DQS falling edge crossed Vref to when the Ck rising edge crosses Vref. Essentially the time between the two trace labels is measured. The minimum value is the measured value for tDSS min and is reported in mtCK(avg). This test is considered informational only since the limit is undefined.

- **tDQDQS** (P2) is measuring the skew between DQ and DQS. Since this measurement is performed once per burst, this shows how many Write bursts were in the acquired waveform.

- **t@tDSSmin** (P4) displays the location of where the minimum value of tDSS occurred. This is used to position the zoom traces at the location of the "worst case results".

### Timing Tests on CA/ADDR

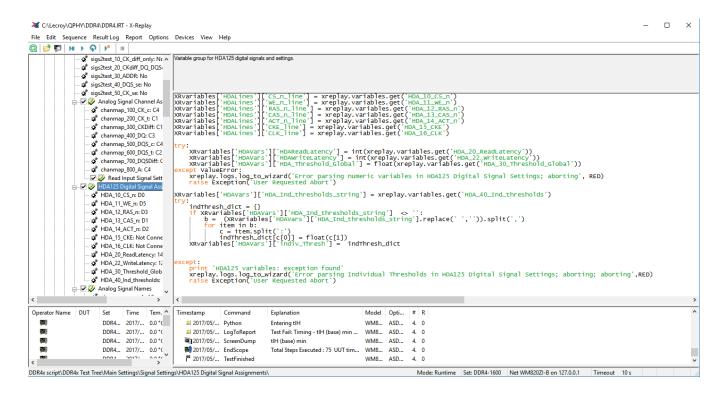

### tIS (base) (DDR4 only)

This test measures the setup time between a command or address line at VIL(AC) and CK\_t/CK\_c crossing or at CKdiff=0 V.

### tIH (base) (DDR4 only)

This test measures the setup time between a command or address line at VIL(DC) and CK\_t/CK\_c crossing or at CKdiff=0 V.

### TcIPW (LPDDR4 only)

This test measures the Command Address input pulse width in reference to the Vcent\_CA (pin mid). There are different minimum pulse widths allowed by speed grade, and QPHY-DDR4 checks for this.

### Timing Tests on Pre/Postamble (using interpolation)

#### tWPRE and tWPST

These tests characterize the Preamble and Postamble times for all Write bursts detected in the acquisition. Both tests use an interpolation algorithm to determine the point where the signal begins, which depending upon the signal shape can lead to some inaccuracies. Only tWPST is shown below.

- tWPRE measures the timing between when preamble starts (DQS comes out of idle) and where the preamble ends (DQS at Vref).

- tWPST measures the timing between when the postamble starts (DQS at Vref) and where the postamble ends (DQS begins to returns to idle).

At the completion of the tWPST test, the oscilloscope is in the following state:

Figure 24. Oscilloscope configuration after the tWPST test.

#### Shown on the screen:

• **Z2** is a zoom of F2, the acquired DQS signal after any probe deskew has been applied. The zoom is positioned at the location of the "worst case" tWPST measurement indicated by t@tWPSTmin. A trace label is applied to indicate where the interpolation algorithm has determined where the device is no longer driving and Vref.

- **tWPST** (P1) is measuring the time from DQS begins to return to idle to the last falling edge on DQS at Vref. The low level quit time found through interpolation is marked by the trace label. Essentially the time between the two trace labels is measured. The minimum value is the measured value for tWPST min reported in mtCK(avg). This test is considered informational only since the limit is undefined.

- **tDQDQS** (P2) is measuring the skew between DQ and DQS. Since this measurement is performed once per burst, this shows how many Write bursts were in the acquired waveform.

- t@tWPSTmin (P4) displays the location of where the minimum value of tWPST occurred. This is used to position the zoom traces at the location of the "worst case results".

# **Timing Tests on Read Bursts (Outputs)**

# Timing Tests on Bits (not using interpolation)

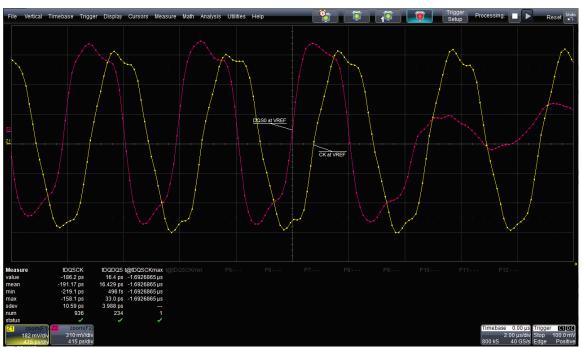

#### **tDQSQ**

The tDQSQ is a timing test, defined as the total skew between the DQS crossing (DQS\_t and DQS\_c) and the widest DQ edge of a Read output burst (in the same DQS group). The scope software measures the maximum skew between DQS/DQ in the same DQS packet and determine if the value is within the max limit set by the JEDEC standard.

Figure 25. Oscilloscope tDQSQ test - largest DQS to DQ skew.

#### tQSH and tQSL