# PCI<sup>®</sup> Gen4 OCuLink to PCIe Host Adapter User Manual and *Quick Start Guide*

#### **Before Starting**

Use this document for quick installation and setup. If you experience problems or need more information, see the product manuals available at the Teledyne LeCroy web site <a href="https://teledynelecroy.com/sw/pciexpress">https://teledynelecroy.com/sw/pciexpress</a>

### 1 Introduction

Teledyne LeCroy's PCIe Gen4 OCuLink Host Adapter provides developers with multiple test capabilities to speed development of new PCIe OCuLink Cable designs by allowing connection of an OCuLink device to be connected directly to a standard PCIe x16 CEM Slot. It supports data rates of 2.5 GT/s, 5.0 GT/s, 8.0 GT/s and 16.0 GT/s. Several test points and headers provide easy access to check status of bus signals.

The PCIe Gen4 OCuLink Host Adapter card works with the PCIe Gen4 OCuLink Cable (or set of cables) up to 0.6 meter in length as defined in the PCI Express® OCuLink Cable Specification.

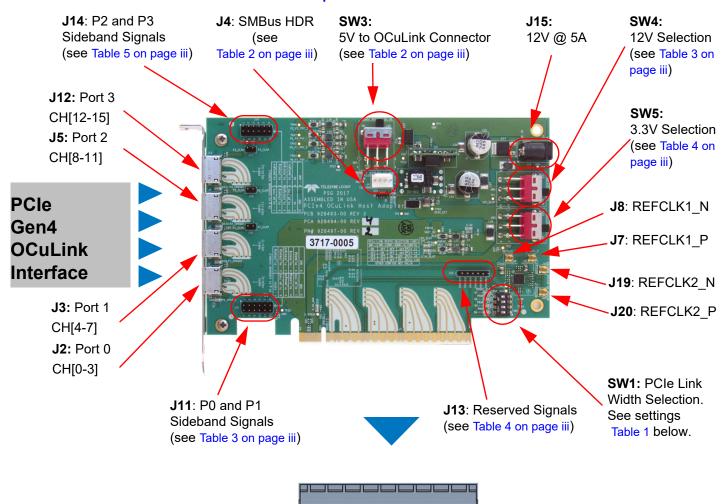

#### PCle Gen4 OCuLink Host Adapter

### **2** Components

The adapter package includes the following components:

- PCIe Gen4 OCuLink to PCIe Host Adapter

- DC Power Adapter (12V @ 5A)

- User Manual and Quick Start Guide (this document)

Inspect the received shipping container for any damage. Unpack the container and account for each of the system components listed on the accompanying packing list. Visually inspect each component for absence of damage.

In the event of damage, notify the shipper and Teledyne LeCroy. Retain all shipping materials for shipper's inspection.

## 3 Connections

#### PCle Gen4 OCuLink Host Adapter: Interconnection Overview

### Host PCIe x16 CEM Slot

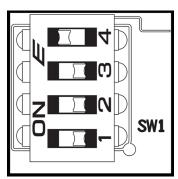

### Switch Configuration: SW1, SW3, SW4, SW5

**Table 1: PCle Link Width Configurations**

| SW1-1 | SW1-2 | SW1-3 | SW1-4 | PCIe Bus Link Width   |

|-------|-------|-------|-------|-----------------------|

| ON    | OFF   | OFF   | OFF   | x1                    |

| OFF   | ON    | OFF   | OFF   | x4                    |

| OFF   | OFF   | ON    | OFF   | x8                    |

| OFF   | OFF   | OFF   | ON    | x16 (default setting) |

Note 1: Other switch configurations not valid.

Table 2: Switch Settings for 5V\_EXT: SW3

| SW3 | 5V_EXT Selector Switch to OCuLink Connector |  |

|-----|---------------------------------------------|--|

| OFF | No 5V_EXT to OCuLink Connector              |  |

| ON  | 5V_EXT to OCuLink Connector                 |  |

**Notes:** Factory settings for the switch is OFF. 5V is optional on OCuLink External cables. If 5V needs to be provided use the external power supply and set SW3 to ON.

Table 3: Switch Settings for 12V: SW4

| SW4      | 12V to EXT or Host           |

|----------|------------------------------|

| 12V Host | 12V from PCIe Slot Connector |

| 12V EXT  | 12V from DC Jack input       |

Note: Factory settings for the switch is 12V Host.

Table 4: Switch Settings for 3.3V: SW5

| SW5       | 3.3V to EXT or Host                        |  |

|-----------|--------------------------------------------|--|

| 3.3V Host | 3.3V from PCIe Slot Connector              |  |

| 3.3V EXT  | 3.3V derived from 12V DC Jack input supply |  |

**Notes:** Factory settings for the switch is 3.3V Host. External power supply needs to be connected only when using OCuLink External cables.

# **5** Connector Signals

**Table 2: J4 SMBus Connections**

| PIN | DESCRIPTION          |  |

|-----|----------------------|--|

| 1   | DGND                 |  |

| 2   | I2C_SDA_EXT          |  |

| 3   | I2C_SCL_EXT          |  |

| 4   | VCC (+3.3V to +5.0V) |  |

Table 3: J11 P0 and P1 Sideband Signals

| PIN | DESCRIPTION | PIN | DESCRIPTION |

|-----|-------------|-----|-------------|

| 1   | P1_CPRSNT#  | 7   | P3P3V       |

| 2   | P0_CPRSNT#  | 8   | P1_BP_TYPE  |

| 3   | P1_PERST#IN | 9   | P1_WAKE#IN  |

| 4   | P0_PERST#   | 10  | P0_CLKREQ#  |

| 5   | P0_WAKE#    | 11  | P0_BP_TYPE  |

| 6   | GND         | 12  | GND         |

**Table 4: J13 PCIe CEM Slot Signals**

| PIN | DESCRIPTION |

|-----|-------------|

| 1   | RSVDA19     |

| 2   | RSVDA32     |

| 3   | RSVDA33     |

| 4   | RSVDA50     |

| 5   | RSVDA30     |

| 6   | RSVDA82     |

Table 5: J14 P2 and P3 Sideband Signals

|     |             |     | •           |

|-----|-------------|-----|-------------|

| PIN | DESCRIPTION | PIN | DESCRIPTION |

| 1   | P3_WAKE#IN  | 7   | P3_BP_TYPE  |

| 2   | P2_CPRSNT#  | 8   | P3_CPRSNT#  |

| 3   | P2_PERST#IN | 9   | P3_PERST#IN |

| 4   | P2_WAKE#IN  | 10  | P2_BP_TYPE  |

| 5   | NC          | 11  | NC          |

| 6   | GND         | 12  | GND         |

Table 9: PCIe Gen4 OCuLink Host Adapter Test Points and Functions

| Function          |  |  |

|-------------------|--|--|

| 12V_SLOT          |  |  |

| 3.3VAUX           |  |  |

| 3.3V_SLOT         |  |  |

| GND               |  |  |

| 5V                |  |  |

| SMBus_DATA        |  |  |

| SMBus_CLK         |  |  |

| P3P3V_VACT_TX     |  |  |

| P3P3V_EXT         |  |  |

| P3P3V_VACT_RX     |  |  |

| 5V Port 0, Port 1 |  |  |

| 5V Port 0, Port 1 |  |  |

| 5V Port 2, Port 3 |  |  |

| 5V Port 2, Port 3 |  |  |

|                   |  |  |

### 7 Environmental Conditions

- Temperature: Operating 32° F to 122° F (0° C to 50° C)

- Temperature: Non-Operating 14° F to 176° F (-10° C to 80° C)

- Humidity: Operating 10% to 90% RH (non-condensing)

#### **Teledyne LeCroy Customer Support**

Online Download

Periodically check the Teledyne LeCroy Protocol Solutions Group web site for software updates and other support related to this product. Software updates are available to users with a current Maintenance Agreement.

Web: <u>teledynelecroy.com/sw/pciexpress</u>

E-mail: <u>psgsupport@teledyne.com</u>

Support: <u>teledynelecroy.com/support/contact</u>

#### Trademarks and Servicemarks

### Teledyne LeCroy is a trademark of Teledyne LeCroy. All other trademarks are property of their respective companies.

#### Changes

Product specifications are subject to change without notice. Teledyne LeCroy reserves the right to revise the information in this document without notice or penalty.